Interested Article - Кольца защиты

- 2021-08-29

- 1

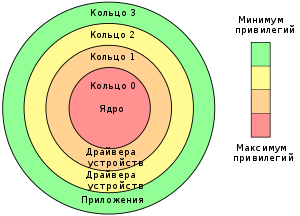

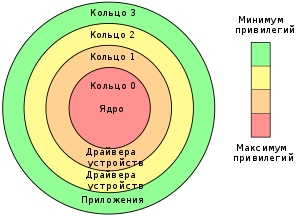

Кольца защиты — архитектура информационной безопасности и функциональной отказоустойчивости , реализующая аппаратное разделение системного и пользовательского уровней привилегий. Структуру привилегий можно изобразить в виде нескольких концентрических кругов. В этом случае системный режим ( режим супервизора или нулевое кольцо, так называемое «кольцо 0»), обеспечивающий максимальный доступ к ресурсам, является внутренним кругом, тогда как режим пользователя с ограниченным доступом — внешним. Традиционно семейство микропроцессоров x86 обеспечивает четыре кольца защиты.

Архитектуре колец защиты обычно противопоставляют системы, основанные на мандатной адресации, обеспечивающей доступ к объекту по его описанию ( англ. ).

Реализация

Поддержка нескольких колец защиты была одной из революционных концепций, включённых в операционную систему Multics , предшественника сегодняшних UNIX-подобных операционных систем. Однако, большинство UNIX-систем использует только 2 кольца, даже если аппаратные средства поддерживают больше режимов центрального процессора .

Многие современные архитектуры центральных процессоров (включая популярную архитектуру x86 ) включают некоторые формы защиты. Но несмотря на это, операционная система Windows NT , также как и UNIX , полностью не используют эти возможности. Предшественница Windows NT, операционная система OS/2 , использовала три кольца: кольцо 0 для кода ядра и драйверов устройств, кольцо 2 для привилегированного кода (программы с доступом к операциям ввода-вывода), и кольцо 3 для непривилегированного кода (почти все пользовательские программы).

Оригинальная система Multics имела восемь колец защиты, но многие современные системы имеют, как правило, меньше. Процессор всегда знает, в каком кольце исполняется код, благодаря специальным машинным регистрам. В некоторых системах области виртуальной памяти также связаны с номерами колец, и более привилегированному кольцу даются специальные права (такие, как адресация реальной памяти в обход механизма виртуальной памяти).

Механизм колец строго ограничивает пути, с помощью которых управление можно передать от одного кольца к другому, а также предписывает ограничения на операции доступа к памяти, которые могут быть произведены внутри кольца. Обычно существует некоторая инструкция (шлюз), которая передаёт контроль из менее защищённого в более защищённое (с меньшим номером) кольцо; это известно как запрос супервизора во многих операционных системах, использующих кольцевую архитектуру. Этот механизм разработан для того, чтобы ограничить возможности случайного или намеренного нарушения безопасности.

Защита кольца может сочетаться с режимами процессора (режим master/kernel/privileged против режима slave/user/unprivileged) в некоторых системах. Операционные системы, выполняющиеся на аппаратном обеспечении, поддерживающем такие режимы, могут использовать оба способа защиты или только один из них.

Эффективное использование архитектуры колец защиты требует тесного взаимодействия между аппаратными средствами и операционной системой. Операционные системы, разрабатывающиеся так, чтобы они работали на большом количестве платформ, могут иметь различную реализацию механизма колец на каждой платформе. Часто модель безопасности упрощают до двух уровней доступа: уровня «ядра» и уровня «пользователя», даже если аппаратные средства обеспечивают большую степень детализации уровней выполнения.

Режим супервизора

Термином режим супервизора ( Supervisor mode ) разработчики и производители процессоров, как правило, называют наиболее привилегированный режим работы процессора. Чаще всего этот режим используется для выполнения кода ядра операционной системы. Обычно этот режим по функциональности соответствует 0-му кольцу защиты (Ring 0) в x86-процессорах, то есть предоставляет неограниченный доступ ко всем возможностям процессора, работе с периферией и так далее. Код, работающий в данном режиме, как правило, занимается управлением доступными аппаратными ресурсами, разделением их использования между отдельными задачами (процессами) и так далее, что и привело к такому названию режима.

Некоторые фирмы-разработчики и производители процессоров, например ARM, не используют классификацию режимов работы процессора в виде колец защиты. Тем не менее, у большинства современных процессоров (кроме простейших), как правило, присутствует несколько режимов работы, отличающихся друг от друга доступными в данном режиме привилегиями.

Режим гипервизора

Некоторые современные процессоры могут предоставлять дополнительный режим работы, известный как режим гипервизора ( Hypervisor mode ). Как правило, данный режим реализуется с целью поддержки технологий виртуализации на уровне аппаратного обеспечения. Это позволяет достигнуть не только одновременного выполнения нескольких задач, но и одновременного выполнения нескольких операционных систем на одном процессоре без существенных потерь производительности и без изменения самих операционных систем. Как правило, при использовании данного режима полный доступ ко всем ресурсам возможен именно из режима гипервизора. В таком случае режим супервизора уже не является максимально привилегированным и ограничивает многие привилегированные операции. При выполнении привилегированных операций операционными системами в режиме супервизора управление передается специальной программе — гипервизору . Гипервизор осуществляет арбитраж использования имеющихся аппаратных ресурсов несколькими операционными системами аналогично тому, как сами операционные системы осуществляют распределение ресурсов между несколькими задачами. По сути, гипервизор обычно является небольшим ядром, которое управляет распределением ресурсов между несколькими операционными системами и работает уровнем ниже, чем сами операционные системы. В силу этого в терминологии x86 данный режим часто условно называют кольцом −1 (Ring −1).

Режим системного управления (SMM)

Режим системного управления (System Management Mode) — самый привилегированный режим выполнения на процессорах архитектуры x86 / x86-64 (впервые появился в 386SL ). Режим SMM (условно называемый «Кольцо -2») более привилегированный, чем «Кольцо 0» и аппаратный гипервизор ( VT/AMD-v ) «Кольцо -1». В этом режиме приостанавливается нормальное выполнение кода, и начинается выполнение специального кода из системного ОЗУ (SMRAM), недоступного в других режимах. Этот код получает доступ ко всей системной памяти, включая ядро и память гипервизора.

Йоанна Рутковская опубликовала информацию об уязвимости « Blue Pill », позволяющей выполнить произвольный код в режиме SMM.

Модель взаимодействия между ЦП и уровнями абстракции ОС

Впервые режим SMM был реализован в МП 80386SL и i486SL. Начиная с Intel-486, этот режим стал обязательным элементом архитектуры IA-32. Режим SMM предназначен для выполнения некоторых действий с возможностью их полной изоляции от операционной системы. Процессор переходит в этот режим только аппаратно по сигналу SMI#. Никакого программного способа для перехода в этот режим не предусмотрено. При возникновении SMI-прерывания код SMI обработчика выполняется в отдельном адресном пространстве (SMRAM). На время перехода в SMI режим контекст прерванного процесса сохраняется. Во время выполнения SMM-обработчика все прерывания отключены. Код SMI-обработчика может выполняться только в SMRAM-памяти.

В 2006 году Лоик Дюфло (Loïc Duflot) представил очень любопытную атаку против механизма уровней безопасности OpenBSD, которая использовала режим SMM. В то время SMM-режим не был защищен и существовала возможность записать в SMRAM произвольный код. Но затем производители систем начали защищать режим SMM. Для хранения исполняемого в SMM кода была выделена специальная область памяти, названная SMRAM, которая получила особую защиту со стороны чипсета (Memory Controller Hub, если быть точным). На большинстве современных систем уже весьма нетривиально выполнить код с привилегиями SMM. Для этого нужно найти «дыру» в чипсете или BIOS'е (даже если у нас есть доступ на уровне ядра). На самом деле, на Black Hat 2008 в Лас-Вегасе Шерри Спаркс (Sherri Sparks) и Шон Эмблтон (Shawn Embleton) сделали презентацию о руткитах SMM, но при этом ясно дали понять, что их руткиты можно загрузить только на старых системах (до 2006 года). Также на конференции обсуждалась «дыра» в BIOS Intel, которая позволяла выполнять произвольный код в режиме SMM. Затем были обнаружены ещё два способа пробиться в режим SMM на различных системах. Другая атака, которую обнаружили в конце 2008 года, срабатывала на большом количестве систем Intel (и потенциально на машинах со старыми BIOS).

Руткиты SMM (или руткиты кольца −2) требуют доступа к сильно защищённой памяти SMM, и на большинстве современных систем атакующему придётся использовать «дыры» (найти их весьма нетривиально).

Атаки SMM разрабатываются под конкретную версию BIOS (или линейку BIOS) и семейство чипсетов, например, для линеек 3-й или 4-й серии чипсетов Intel (т. е. атаки на Q35 и Q45 либо атаки на AMI и AWARD BIOS различны).

Intel vPro / Active Management Technology

Invisible Things Lab предложила называть функциональность технологии Intel vPro / Intel AMT кольцом -3. В рамках этой технологии чипсеты, поддерживающие технологию vPro, содержат независимый микропроцессор (архитектура ARC 4), имеют отдельный интерфейс к сетевой карте, эксклюзивный доступ к выделенному участку ОЗУ (16 МБ), DMA-доступ к основной ОЗУ. Программы на нём выполняются независимо от центрального процессора, прошивка хранится совместно с кодами BIOS либо на аналогичной флеш-памяти SPI (код имеет криптографическую подпись). Частью прошивки является встроенный веб-сервер. По умолчанию AMT выключен, но часть кода все же работает в этом режиме даже при выключенном AMT. Код кольца -3 активен даже в режиме питания S3 Sleep.

См. также

Примечания

- . PDF (3.93 MB)

- от 6 января 2019 на Wayback Machine // Alexander Tereshkin, Rafal Wojtczuk; BH 29.07.2009

Ссылки

- . InsidePro Software. Дата обращения: 25 марта 2010. Архивировано из 25 февраля 2012 года.

- 2021-08-29

- 1