Interested Article - Флеш-память

- 2021-09-22

- 1

Флеш ( англ. flash memory ) — разновидность полупроводниковой технологии электрически перепрограммируемой памяти ( EEPROM ). Это же слово используется в электронной схемотехнике для обозначения технологически законченных решений постоянных запоминающих устройств в виде микросхем на базе этой полупроводниковой технологии. В быту это словосочетание закрепилось за широким классом твердотельных устройств хранения информации.

Эта статья о полупроводниковой технологии и связанных с ней электронных компонентах; о твердотельных накопителях есть другие статьи: карта памяти , USB-флеш-накопитель .

Благодаря компактности, дешевизне, механической прочности, большому объёму, скорости работы и низкому энергопотреблению флеш-память широко используется в цифровых портативных устройствах и носителях информации . Серьёзным недостатком данной технологии является ограниченный ресурс носителей , а также чувствительность к электростатическому разряду.

История

Предшественниками технологии флеш-памяти можно считать ультрафиолетово-стираемые постоянные запоминающие устройства ( EPROM ) и электрически стираемые ПЗУ ( EEPROM ). Эти приборы также имели матрицу транзисторов с плавающим затвором , в которых инжекция электронов в плавающий затвор («запись») осуществлялась созданием большой напряжённости электрического поля в тонком диэлектрике. Однако площадь разводки компонентов в матрице резко увеличивалась, если требовалось создать поле обратной напряжённости для снятия электронов с плавающего затвора («стирания»), поэтому и возникло два класса устройств: в одном случае жертвовали цепями стирания, получая память высокой плотности с однократной записью, а в другом случае делали полнофункциональное устройство с гораздо меньшей ёмкостью.

Соответственно, усилия инженеров были направлены на решение проблемы плотности компоновки цепей стирания. Они увенчались успехом — изобретением инженера компании Toshiba Фудзи Масуокой в 1984 году. Название «флеш» было придумано также в Toshiba — , которому процесс стирания содержимого памяти напомнил фотовспышку ( англ. flash ). Масуока представил свою разработку в 1984 году на конференции IEEE International Electron Devices Meeting (IEDM), проходившей в Сан-Франциско .

В 1988 году Intel выпустила первый коммерческий флеш-чип NOR-типа.

NAND-тип флеш-памяти был анонсирован Toshiba в 1989 году на International Solid-State Circuits Conference .

Принцип работы

Основным компонентом в флеш-памяти является транзистор с плавающим затвором , который является разновидностью МОП-транзисторов . Его отличие в том, что у него есть дополнительный затвор (плавающий), расположенный между управляющим затвором и p-слоем. Плавающий затвор изолирован, и хранимый в нём отрицательный заряд будет оставаться надолго.

SLC и MLC

Различают устройства, в которых элементарная ячейка хранит один бит информации или несколько бит. В однобитовых ячейках различают только два уровня заряда на плавающем затворе. Такие ячейки называют одноуровневыми ( single-level cell, SLC ). В многобитовых ячейках различают больше уровней заряда; их называют многоуровневыми ( multi-level cell, MLC ). MLC-устройства дешевле и более ёмки, чем SLC-устройства, однако имеют более высокое время доступа и примерно на порядок меньшее максимальное количество перезаписей .

Обычно под MLC понимают память с 4 уровнями заряда (2 бита) на каждую ячейку. Более дешёвую в пересчёте на объём память с 8 уровнями (3 бита) называют TLC ( Triple Level Cell ) или 3bit MLC (так называет ее Samsung) . Существуют также устройства с 16 уровнями на ячейку (4 бита), QLC ( quad-level cell ). В августе 2018 года Samsung Electronics объявил о начале массового производства SSD на памяти QLC V-NAND .

К 2016 году многоуровневая память доминирует на рынке. Тем не менее, SLC-изделия, несмотря на многократно меньшую ёмкость, продолжают разрабатываться и выпускаться для особо ответственных применений .

Аудиопамять

Естественным развитием идеи MLC-ячеек была мысль записать в ячейку аналоговый сигнал . Наибольшее применение такие аналоговые флеш-микросхемы получили в воспроизведении относительно коротких звуковых фрагментов в дешёвых тиражируемых изделиях. Такие микросхемы могут применяться в простейших игрушках, звуковых открытках, автоответчиках и так далее.

NOR и NAND

Флеш-память различается методом соединения ячеек в массив.

Конструкция NOR использует классическую двумерную матрицу проводников , в которой на пересечении строк и столбцов установлено по одной ячейке. При этом проводник строк подключался к стоку транзистора, а столбцов — ко второму затвору. Исток подключался к общей для всех подложке.

Конструкция NAND — трёхмерный массив. В основе та же самая матрица, что и в NOR, но вместо одного транзистора в каждом пересечении устанавливается столбец из последовательно включенных ячеек. В такой конструкции получается много затворных цепей в одном пересечении. Плотность компоновки можно резко увеличить (ведь к одной ячейке в столбце подходит только один проводник затвора), однако алгоритм доступа к ячейкам для чтения и записи заметно усложняется. Также в каждой линии установлено два МОП-транзистора: управляющий транзистор разрядной линии ( англ. bit line select transistor ), расположенный между столбцом ячеек и разрядной линией и управляющий транзистор заземления, расположенный перед землёй ( англ. ground select transistor ).

Технология NOR позволяет получить быстрый доступ индивидуально к каждой ячейке, однако площадь ячейки велика. Наоборот, NAND имеют малую площадь ячейки, но относительно длительный доступ сразу к большой группе ячеек. Соответственно, различается область применения: NOR используется как для непосредственной памяти программ микропроцессоров, так и для хранения небольших вспомогательных данных.

Названия NOR и NAND произошли по ассоциации схемы включения ячеек в массив со схемотехникой микросхем КМОП -логики — NOR - и NAND -элементов.

NAND чаще всего применяется для USB-флеш-накопителей , карт памяти, SSD ; а NOR — во встраиваемых системах .

Существовали и другие варианты объединения ячеек в массив, но они не прижились.

-

Программирование флеш-памяти

Программирование флеш-памяти -

Стирание флеш-памяти

Стирание флеш-памяти

Чтение

Для чтения подаётся положительное напряжение на управляющий затвор. Если в плавающем затворе отсутствует заряд, то транзистор начнёт проводить ток. В противном случае ток между истоком и стоком не возникает. Для MLC-ячеек необходимо произвести несколько измерений.

- NOR

Для чтения определённой ячейки памяти необходимо подать на её управляющий затвор промежуточное напряжение (достаточное для проводимости транзистора только при отсутствии заряда в плавающем затворе). На остальные ячейки в линии следует подать минимальное напряжение для исключения проводимости этих ячеек. Если в интересующей нас ячейке отсутствует заряд, то возникнет ток между разрядной линией ( англ. bit line ) и землёй.

- NAND

В данной компоновке также подаётся промежуточное напряжение на управляющий затвор определённой ячейки. На остальные управляющие затворы в линии подаётся повышенное напряжение, чтобы они гарантированно проводили ток. Таким образом возникает ток между землёй и линией, если в интересующей нас ячейке отсутствует заряд.

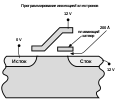

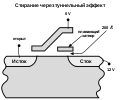

Запись

Для записи заряды должны попасть в плавающий затвор, однако он изолирован слоем оксида. Для перенесения зарядов может использоваться эффект туннелирования . Для разряда необходимо подать большое положительное напряжение на управляющий затвор: отрицательный заряд с помощью туннельного эффекта покинет плавающий затвор. И наоборот, для заряда плавающего затвора необходимо подать большое отрицательное напряжение.

Также запись может быть реализована с помощью . При протекании тока между истоком и стоком повышенного напряжения электроны могут преодолевать слой оксида и оставаться в плавающем затворе. При этом необходимо, чтобы на управляющем затворе присутствовал положительный заряд, который создавал бы потенциал для инжекции.

В MLC для записи разных значений используются разные напряжения и время подачи .

Каждая запись наносит небольшой ущерб оксидному слою, поэтому число записей ограничено.

Запись в NOR- и NAND-компоновке состоит из двух стадий: вначале все транзисторы в линии устанавливаются в 1 (отсутствие заряда), затем нужные ячейки устанавливаются в 0.

- NOR

На первой стадии очистка ячеек происходит с помощью туннельного эффекта: на все управляющие затворы подаётся сильное напряжение. Для установки конкретной ячейки в 0 используется инжекция горячих носителей. На разрядную линию подаётся большое напряжение. Вторым важным условием этого эффекта является наличие положительных зарядов на управляющем затворе. Положительное напряжение подаётся лишь на некоторые транзисторы, на остальные транзисторы подаётся отрицательное напряжение, таким образом ноль записывается только в интересующие нас ячейки.

- NAND

Первая стадия в NAND аналогична NOR. Для установки нуля в ячейку используется туннельный эффект, в отличие от NOR. На интересующие нас управляющие затворы подаётся большое отрицательное напряжение.

3D NAND

Схемотехника NAND оказалась удобна для построения вертикальной компоновки блока ячеек на кристалле . На кристалл послойно напыляют проводящие и изолирующие слои, которые образуют проводники затворов и сами затворы. Затем в этих слоях формируют множество отверстий на всю глубину слоев. На стенки отверстий наносят структуру полевых транзисторов — изоляторы и плавающие затворы. Таким образом формируют столбец кольцеобразных полевых транзисторов с плавающими затворами.

Такая вертикальная структура оказалась очень удачна и обеспечила качественный рывок плотности флеш-памяти. Некоторые компании продвигают технологию под своими торговыми марками, например, V-NAND, BiCS. Количество слоёв по мере развития технологии наращивается: так, на 2016 год количество слоёв ряда изделий достигло 64 , в 2018 году освоено производство 96-слойной памяти , в 2019 году Samsung заявила о серийном освоении 136-слойных кристаллов . В 2021 году производители планировали перейти на 256 слоев, а к 2023 году - на 512, это позволит размещать на одном флеш-чипе до 12 терабайт данных . В конце июля 2022 года американская компания Micron Technology первой в мире выпустила 232-слойную память формата NAND (TLC-память с шестью плоскостями с возможностью независимого считывания в каждой плоскости) , а уже через неделю, в начале августа 2022 года, Hynix побила этот рекорд, выпустив 238-слойную флеш-память ..

Многокристальные микросхемы

Для экономии места в одну микросхему флеш-памяти может упаковываться несколько полупроводниковых пластин (кристаллов), до 16 штук .

Технологические ограничения

Запись и чтение ячеек различаются в энергопотреблении: устройства флеш-памяти потребляют большой ток при записи для формирования высоких напряжений, тогда как при чтении затраты энергии относительно малы.

Ресурс записи

Изменение заряда сопряжено с накоплением необратимых изменений в структуре и потому количество записей для ячейки флеш-памяти ограничено. Типичные количества циклов стирания-записи составляют от тысячи или менее до десятков и сотен тысяч, в зависимости от типа памяти и технологического процесса. Гарантированный ресурс значительно более низок при хранении нескольких бит в ячейке (MLC и TLC) и при использовании техпроцессов класса « 30 нм » и более современных.

Одна из причин деградации — невозможность индивидуально контролировать заряд плавающего затвора в каждой ячейке. Дело в том, что запись и стирание производятся над множеством ячеек одновременно — это неотъемлемое свойство технологии флеш-памяти. Автомат записи контролирует достаточность инжекции заряда по референсной ячейке или по средней величине. Постепенно заряд отдельных ячеек рассогласовывается и в некоторый момент выходит за допустимые границы, которые может скомпенсировать инжекцией автомат записи и воспринять устройство чтения. Понятно, что на ресурс влияет степень идентичности ячеек. Одно из следствий этого — с уменьшением топологических норм полупроводниковой технологии создавать идентичные элементы все труднее, поэтому вопрос ресурса записи становится все острее.

Другая причина — взаимная диффузия атомов, изолирующих и проводящих областей полупроводниковой структуры, ускоренная градиентом электрического поля в области кармана и периодическими электрическими пробоями изолятора при записи и стирании. Это приводит к размыванию границ и ухудшению качества изолятора, уменьшению времени хранения заряда.

Изначально, в 2000-х годах, для 56-нм памяти такой ресурс стираний составлял до 10 тыс. раз для MLC-устройств и до 100 тыс. раз для SLC-устройств, однако с уменьшением техпроцессов количество гарантированных стираний снижалось. Для 34-нм памяти (начало 2010-х годов) обычная 2-битная MLC гарантировала порядка 3—5 тысяч, а SLC — до 50 тысяч . В 2013 отдельные модели гарантировали порядка единиц тысяч циклов для MLC и менее тысячи (несколько сотен) для TLC до начала деградации .

| Тип памяти | Ресурс | Примеры решений |

|---|---|---|

| SLC NOR | 100 000 .. 1 000 000 | Numonyx M58BW, Spansion S29CD016J |

| MLC NOR | 100 000 | Numonyx J3 flash |

| SLC NAND | 100 000 | Samsung OneNAND KFW4G16Q2M |

| MLC NAND | 1000 .. 10 000 | Samsung K9G8G08U0M |

| TLC NAND | 1000 | Samsung SSD 840 |

| 3D MLC NAND | 6000 .. 40 000 | Samsung SSD 850 PRO, Samsung SSD 845DC PRO |

| 3D TLC NAND | 1000 .. 3000 | Samsung SSD 850 EVO, Samsung SSD 845DC EVO, Crucial MX300 |

Идут исследования экспериментальной технологии восстановления ячейки флеш-памяти путём локального нагрева изолятора затвора до 800 °С в течение нескольких миллисекунд.

Срок хранения данных

Изоляция кармана неидеальна, заряд постепенно изменяется. Срок хранения заряда, заявляемый большинством производителей для бытовых изделий, не превышает 10—20 лет [ источник не указан 3750 дней ] , хотя гарантия на носители даётся не более чем на 5 лет. При этом память MLC имеет меньшие сроки, чем SLC.

Специфические внешние условия, например, повышенные температуры или радиационное облучение (гамма-радиация и частицы высоких энергий), могут катастрофически сократить срок хранения данных.

У современных микросхем NAND при чтении возможно повреждение данных на соседних страницах в пределах блока. Осуществление большого числа (сотни тысяч и более) операций чтения без перезаписи может ускорить возникновение ошибки .

По данным Dell, длительность хранения данных на SSD, отключенных от питания, сильно зависит от количества прошедших циклов перезаписи (P/E) и от типа флеш-памяти и в худших случаях может составлять 3—6 месяцев .

Иерархическая структура

Стирание, запись и чтение флеш-памяти всегда происходят относительно крупными блоками разного размера, при этом размер блока стирания всегда больше, чем блок записи, а размер блока записи не меньше, чем размер блока чтения. Собственно, это — характерный отличительный признак флеш-памяти по отношению к классической памяти EEPROM .

Как следствие — все микросхемы флеш-памяти имеют ярко выраженную иерархическую структуру. Память разбивается на блоки, блоки состоят из секторов, секторы — из страниц. В зависимости от назначения конкретной микросхемы глубина иерархии и размер элементов могут меняться.

Например, NAND-микросхема может иметь размер стираемого блока в сотни кбайт, размер страницы записи и чтения — 4 кбайт. Для NOR-микросхем размер стираемого блока варьируется от единиц до сотен кбайт, размер сектора записи — до сотен байт, страницы чтения — единицы—десятки байт.

Скорость чтения и записи

Время стирания варьируется от единиц до сотен миллисекунд в зависимости от размера стираемого блока. Время записи — десятки-сотни микросекунд.

Обычно время чтения для NOR-микросхем нормируется в десятки наносекунд. Для NAND-микросхем время чтения составляет десятки микросекунд.

Технологическое масштабирование

Из-за своей высокорегулярной структуры и высокого спроса на большие объёмы техпроцесс при изготовлении флеш-памяти NAND уменьшается более быстро, чем для менее регулярной DRAM-памяти и почти нерегулярной логики (ASIC). Высокая конкуренция между несколькими ведущими производителями лишь ускоряет этот процесс . В варианте закона Мура для логических микросхем удвоение количества транзисторов на единицу площади происходит за три года, тогда как NAND-флеш показывала удвоение за два года. В 2012 году 19-нм техпроцесс был освоен совместным предприятием Toshiba и SanDisk . В ноябре 2012 года Samsung также начала производство по техпроцессу 19 нм (активно используя в маркетинговых материалах фразу «10nm-class», обозначавшую какой-то процесс из диапазона 10—19 нм) .

| ITRS или компания | 2010 | 2011 | 2012 | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 |

|---|---|---|---|---|---|---|---|---|---|

| ITRS Flash Roadmap 2011 | 32 нм | 22 нм | 20 нм | 18 нм | 16 нм | ||||

| ITRS Flash Roadmap 2013 | 17 нм | 15 нм | 14 нм | ||||||

|

Samsung

Samsung 3D NAND (CTF) |

35-32 нм | 27 нм | 21 нм (MLC, TLC) | 19 нм |

19-16 нм

V-NAND (24L) |

12 нм

V-NAND (32L) |

16-10 нм | 12-10 нм | 12-10 нм |

| Micron, Intel | 34-25 нм | 25 нм | 20 нм (MLC + HKMG) | 20 нм (TLC) | 16 нм |

16 нм

3D-NAND |

16 нм

3D-NAND Gen2 |

12 нм

3D-NAND |

12 нм

3D-NAND |

| Toshiba, Sandisk | 43-32 нм | 24 нм | 19 нм (MLC, TLC) | A-19 нм | 15 нм |

15 нм

3D NAND BiCS |

15 нм

3D NAND BiCS |

12 нм

3D NAND |

12 нм

3D NAND |

| SK Hynix | 46-35 нм | 26 нм | 20 нм (MLC) | 20 нм | 16 нм |

16 нм

3D V1 |

16 нм | 12 нм | 12 нм |

Уменьшение техпроцесса позволяло быстро наращивать объёмы чипов памяти NAND-флеш. В 2000 году флеш-память по технологии 180 нм имела объём данных в 512 Мбит на кристалл, в 2005 — 2 Гбит при 90 нм. Затем произошёл переход на MLC, и в 2008 чипы имели объём 8 Гбит (65 нм) . На 2010 год около 25—35 % чипов имели размер 16 Гбит, 55 % — 32 Гбит . В 2012—2014 годах в новых продуктах широко использовались кристаллы объёмом 64 Гбит и начиналось внедрение 128-Гбитовых модулей (10 % на начало 2014 года), изготовленных по техпроцессам 24—19 нм .

По мере уменьшения техпроцесса и его приближению к физическим пределам текущих технологий изготовления , в частности, фотолитографии , дальнейшее увеличение плотности данных может быть обеспечено переходом на большее количество бит в ячейке (например, переход с 2-битной MLC на 3-битную TLC), заменой FG -технологии ячеек на CTF технологию или переходом на трёхмерную компоновку ячеек на пластине (3D NAND, V-NAND; однако при этом увеличивается шаг техпроцесса). Например, приблизительно в 2011—2012 годах всеми производителями были внедрены воздушные промежутки между управляющими линиями, позволившие продолжить масштабирование далее 24—26 нм , а Samsung с 2013—2014 года начала массовый выпуск 24- и 32-слойной 3D NAND на базе CTF технологии , в том числе, в варианте с 3-битными (TLC) ячейками . Проявляющееся с уменьшением техпроцесса уменьшение износостойкости (ресурса стираний), а также увеличение темпа битовых ошибок потребовало применения более сложных механизмов коррекции ошибок и снижения гарантированных объёмов записи и гарантийных сроков . Однако, несмотря на принимаемые меры, вероятно, возможности дальнейшего масштабирования NAND-памяти будут экономически не оправданы или физически невозможны. Исследуется множество возможных замен технологии флеш-памяти, в частности, FeRAM , MRAM , PMC, PCM , ReRAM и т. п.

Особенности применения

Стремление достичь предельных значений ёмкости для NAND-устройств привело к «стандартизации брака» — праву выпускать и продавать микросхемы с некоторым процентом бракованных ячеек и без гарантии непоявления новых «bad-блоков» в процессе эксплуатации. Чтобы минимизировать потери данных, каждая страница памяти снабжается небольшим дополнительным блоком, в котором записывается контрольная сумма , информация для восстановления при одиночных битовых ошибках, информация о сбойных элементах на этой странице и количестве записей на эту страницу.

Сложность алгоритмов чтения и допустимость наличия некоторого количества бракованных ячеек вынудили разработчиков оснастить NAND-микросхемы памяти специфическим командным интерфейсом. Это означает, что нужно сначала подать специальную команду переноса указанной страницы памяти в специальный буфер внутри микросхемы, дождаться окончания этой операции, считать буфер, проверить целостность данных и, при необходимости, попытаться восстановить их.

Слабое место флеш-памяти — количество циклов перезаписи в одной странице. Ситуация ухудшается также в связи с тем, что стандартные файловые системы — то есть стандартные для широко распространённых файловых систем — часто записывают данные в одно и то же место. Часто обновляется корневой каталог файловой системы, так что первые секторы памяти израсходуют свой запас значительно раньше. Распределение нагрузки позволит существенно продлить срок работы памяти .

NAND-контроллеры

Для упрощения применения микросхем флеш-памяти NAND-типа они используются совместно со специальными микросхемами — NAND-контроллерами. Эти контроллеры должны выполнять всю черновую работу по обслуживанию NAND-памяти: преобразование интерфейсов и протоколов, виртуализация адресации (с целью обхода сбойных ячеек), проверка и восстановление данных при чтении, забота о разном размере блоков стирания и записи ( ), забота о периодическом обновлении записанных блоков, равномерное распределение нагрузки на секторы при записи ( ).

Однако, задача равномерного распределения износа не обязательна, поэтому в самых дешевых изделиях ради экономии могут устанавливаться наиболее простые контроллеры. Такие флеш-карты памяти и USB-брелоки быстро выйдут из строя при частой перезаписи. При необходимости очень частой записи данных на флешки предпочтительно использовать дорогие изделия с более износостойкой памятью (MLC вместо TLC, SLC вместо MLC) и качественными контроллерами.

На дорогие NAND-контроллеры также может возлагаться задача «ускорения» микросхем флеш-памяти путём распределения данных одного файла по нескольким микросхемам. Время записи и чтения файла при этом сильно уменьшается.

Специальные файловые системы

Зачастую во встраиваемых применениях флеш-память может подключаться к устройству напрямую — без контроллера. В этом случае задачи контроллера должен выполнять программный NAND-драйвер в операционной системе. Чтобы не выполнять избыточную работу по равномерному распределению записи по страницам, стараются эксплуатировать такие носители со специальными файловыми системами : JFFS2 и YAFFS для Linux и др.

Применение

Существует два основных способа применения флеш-памяти: как носитель информации для компьютеров и электронных гаджетов и как хранилище программного обеспечения (« прошивки ») цифровых устройств. Зачастую эти два применения совмещаются в одном устройстве.

При хранении во флеш-памяти возможно простое обновление прошивок устройств в процессе эксплуатации.

NOR

NOR-флеш наиболее применима в устройствах с энергонезависимой памятью относительно небольшого объёма, требующих быстрого доступа по случайным адресам и с гарантией отсутствия сбойных элементов:

- Встраиваемая память программ однокристальных микроконтроллеров. Типовые объёмы — от 1 кбайта до 1 Мбайта.

- Стандартные микросхемы ПЗУ произвольного доступа для работы вместе с микропроцессором.

- Специализированные микросхемы начальной загрузки компьютеров ( POST и BIOS ), процессоров ЦОС и программируемой логики . Типовые объёмы — единицы и десятки мегабайт.

- Микросхемы хранения среднего размера данных, например, . Обычно снабжаются интерфейсом SPI и упаковываются в миниатюрные корпуса. Типовые объёмы — от сотен кбайт до технологического максимума.

NAND

Там, где требуются рекордные объёмы памяти, NAND-флеш вне конкуренции. Чипы NAND показывали постоянное повышение объёмов, и на 2012 год NAND имел рекордные объёмы на 8-кристальную микросборку в 128 Гбайт (то есть объём каждого кристалла 16 Гбайт или 128 Гбит) .

В первую очередь NAND флеш-память применяется во всевозможных мобильных носителях данных и устройствах, требующих для работы больших объёмов хранения. В основном, это USB-брелоки и карты памяти всех типов, а также мобильные устройства, такие как телефоны, фотоаппараты, медиаплееры.

Флеш-память типа NAND позволила миниатюризировать и удешевить вычислительные платформы на базе стандартных операционных систем с развитым программным обеспечением. Их стали встраивать во множество бытовых приборов: сотовые телефоны и телевизоры, сетевые маршрутизаторы и точки доступа, медиаплееры и игровые приставки, фоторамки и навигаторы.

Высокая скорость чтения делает NAND-память привлекательной для кэширования винчестеров. При этом часто используемые данные операционная система хранит на относительно небольшом твердотельном устройстве, а данные общего назначения записывает на дисковый накопитель большого объёма . Также возможно объединение флеш-буфера на 4—8 ГБ и магнитного диска в едином устройстве, гибридном жёстком диске (SSHD, Solid-state hybrid drive).

Благодаря большой скорости, объёму и компактным размерам, NAND-память активно вытесняет из обращения носители других типов. Сначала исчезли дискеты и дисководы гибких магнитных дисков , снизилась популярность накопителей на магнитной ленте . Магнитные носители практически полностью вытеснены из мобильных и медиаприменений.

Стандартизация

- Низкоуровневые интерфейсы

Стандартизацией корпусов, интерфейсов, системы команд и вопросов идентификации чипов флеш-памяти типа NAND занимается Open NAND Flash Interface (ONFI). Первым стандартом стала спецификация ONFI версии 1.0 , выпущенная 28 декабря 2006 года, за ней последовали ONFI V2.0, V2.1, V2.2, V2.3, V3.0 (2011) . Группа ONFI поддерживается Intel , Micron Technology , Hynix , Numonyx .

Samsung и Toshiba разрабатывают свой, альтернативный ONFI, стандарт Toggle Mode DDR. Первая ревизия выпущена в 2009 году, вторая — в 2010 .

- Высокоуровневые интерфейсы

Помимо стандартизации непосредственно микросхем памяти, идет специфическая формализация доступа к долговременной памяти со стороны распространенных цифровых интерфейсов. Например, группа Non-Volatile Memory Host Controller Interface занимается вопросами стандартизации создания твердотельных дисков для интерфейса PCI Express .

Особняком стоят интегральные решения памяти и контроллера в виде микросхем, например, широко применяется встраиваемая eMMC -память, использующая электрический интерфейс, сходный с MMC , но выполненная в виде микросхемы . Развитием этого интерфейса занимается JEDEC .

Рынок NAND-памяти

Основные производители NAND-флеш-памяти: Micron/Intel, SK Hynix, Toshiba/SanDisk, Samsung. На 2014 год около 35—37 % рынка занимают Toshiba/SanDisk и Samsung. 17 % поставок осуществляет Micron/Intel, ещё 10 — Hynix. Общий объём рынка NAND оценивается примерно в 20—25 млрд долларов США, в год производится от 40 до 60 млрд гигабайт, четверть из которых — встраиваемая eMMC -память. В 2013 году память в основном изготавливалась по техпроцессам в диапазоне 20—30 нм, в 2014 году набирала популярность 19 нм память. Менее 2 % рынка занимала память 3D-NAND от Samsung, другие производители планировали производство 3D NAND с середины 2015 года .

Лишь менее 5 % NAND-памяти, поставлявшейся в 2012—2014 годах, имели однобитные ячейки (SLC), 75 % составляла двухбитная память (MLC) и 15—25 % — трёхбитная память (TLC, в основном Samsung и Toshiba/SanDisk, с середины 2014—2015 годов также и другие) .

Основные производители контроллеров флеш-памяти NAND: Marvell, LSI-SandForce, также производители памяти NAND. Для eMMC контроллеры (eMCP) изготавливают: Samsung, SanDisk, SK Hynix, Toshiba, Micron, Phison, SMI, Skymedi .

См. также

- Универсальный флеш-накопитель

- Charge Trap Flash

- Магниторезистивная оперативная память

- U3

- Восстановление данных

- Файловые системы#Файловые системы для твердотельных накопителей

Примечания

- Simona Boboila, Peter Desnoyers. (англ.) // FAST. — San Jose, California: Northeastern University, 2010. 17 марта 2013 года.

- Hasso Plattner, Alexander. Zeier. . — SpringerLink : Bücher. — Springer, 2012. — С. 45. — 267 с. — ISBN 3-642-29575-4 . 7 мая 2018 года.

- ↑ Kristian Vättö, от 25 июля 2013 на Wayback Machine // Anandtech, February 23, 2012

- ↑ (недоступная ссылка)

- Dennis Martin. . Demartek, Storage Decisions Conference (12 июня 2013). — «MLC typical life 10,000 or fewer write cycles MLC-2: 3,000 – 10,000 write cycles MLC-3: 300 – 3,000 write cycles». Дата обращения: 9 января 2015. 9 января 2015 года.

- Kevin Parrish // Tom’s Hardware, 11 April 2013

- . Дата обращения: 8 августа 2018. 8 августа 2018 года.

- . Дата обращения: 19 ноября 2016. 20 ноября 2016 года.

- от 7 июля 2011 на Wayback Machine ISD ChipCorder

- Thomas Schwarz. . Дата обращения: 12 марта 2017. 1 октября 2017 года.

- . Дата обращения: 11 июля 2016. 8 июля 2016 года.

- . Дата обращения: 19 ноября 2016. 12 ноября 2016 года.

- . Дата обращения: 19 ноября 2016. 20 ноября 2016 года.

- . Дата обращения: 19 ноября 2016. 20 ноября 2016 года.

- . Дата обращения: 8 августа 2018. 8 августа 2018 года.

- от 4 августа 2020 на Wayback Machine // fcenter.ru

- . Дата обращения: 7 сентября 2021. 7 сентября 2021 года.

- от 3 августа 2022 на Wayback Machine от 28 июля 2022 на Wayback Machine // 28.07.2022

- (англ.) . SK hynix (2 августа 2022). Дата обращения: 5 августа 2022. 5 августа 2022 года.

- Геннадий Детинич. . 3DNews (3 августа 2022). Дата обращения: 5 августа 2022. 5 августа 2022 года.

- . Дата обращения: 12 июня 2012. 4 июня 2012 года.

- от 4 марта 2016 на Wayback Machine , IBM 2010 «Table 1. Endurance performance for various technology nodes»

- от 4 марта 2016 на Wayback Machine «Resulting from the continuous reduction of the structure size of the flash memory chips, 2-bit MLC and 3-bit MLC (TLC) NAND flash memory …sometimes only allows 1,000 P/E cycles (MLC) and/or only a few hundred P/E cycles (TLC) per flash memory cell before degradation»; «Table 1: Typical P/E cycles …»

- . Дата обращения: 4 декабря 2012. 4 декабря 2012 года.

- . Дата обращения: 15 октября 2012. Архивировано из 19 июля 2011 года.

- ↑ от 11 сентября 2014 на Wayback Machine , Jim Cooke, 2007 Reducing Read Disturb ""«Rule of thumb for excessive reads per block between ERASE operations: SLC — 1,000,000 READ cycles; MLC — 100,000 READ cycles»

- от 8 октября 2013 на Wayback Machine // Dell: «6. I have unplugged my SSD drive and put it into storage. How long can I expect the drive to retain my data without needing to plug the drive back in? … In MLC and SLC, this can be as low as 3 months and best case can be more than 10 years»

- Kawamatus, Tatsuya . Hagiwara sys-com co., LTD. Дата обращения: 1 августа 2011. (недоступная ссылка)

- ↑ . techinsights (апрель 2013). Дата обращения: 9 января 2015. Архивировано из 9 января 2015 года.

- Clarke, Peter (20 November 2012). от 28 ноября 2012 на Wayback Machine eetimes.com. Retrieved 21 December 2012.

- Anand, Lal Shimpi (2013-07-25). . AnandTech. из оригинала 9 января 2015 . Дата обращения: 9 января 2015 . « Samsung calls its latest NAND process 10nm-class or 1x-nm, which can refer to feature sizes anywhere from 10nm to 19nm but we’ve also heard it referred to as 19nm TLC. »

- . "ObjectiveAnalysis" (июль 2014). Дата обращения: 9 января 2015. 9 января 2015 года. : « .Samsung introduced its 19nm NAND by calling it a „10nm-class“ product. Once again, the press misunderstood and broadcast to the world that Samsung was ahead of all of its competitors »

- . PCWorld. 2013-07-25. из оригинала 9 января 2015 . Дата обращения: 9 января 2015 . : « the 19nm manufacturing process used to produce the NAND. Samsung for some reason is calling this 10nm-class, or 1x NAND, but they assured us that it’s 19nm. »

- от 18 апреля 2012 на Wayback Machine // ITRS 2010

- от 21 января 2015 на Wayback Machine // ITRS из от 21 сентября 2014 на Wayback Machine

- ↑ . techinsights (апрель 2014). Дата обращения: 9 января 2015. Архивировано из 9 января 2015 года.

- ↑ Edward Grochowski, Robert E.Fontana, от 9 января 2015 на Wayback Machine // Flash Memory Summit, 2012 (англ.) : slide 6 «Projected NAND Flash Memory Circuit Density Roadmap»

- ↑ Sean Yang. (англ.) . 2014 NAND Flash Market Update. Supply, Demand and Beyond . TrendForce. Дата обращения: 9 января 2015. 13 января 2015 года.

-

Jeongdong Choe (TechInsights) (2013-07-25).

(англ.)

. EETimes.

из оригинала

12 января 2015

. Дата обращения:

11 января 2015

.

All the NAND manufacturers adopted an air-gap process to achieve high performance and reliability. Toshiba implemented an air-gap process on its 19nm NAND device, while Samsung adopted it on 21nm. IMFT has used a more mature air-gap process on both the wordline and bitline structure since its 25nm NAND technology.

-

Nirmal Ramaswamy, Thomas Graettinger, (Micron) (2013-07-05).

(PDF)

(англ.)

. EE Times-Asia.

(PDF)

из оригинала

12 января 2015

. Дата обращения:

11 января 2015

.

This had already become a problem at the 25nm node requiring the deployment of airgap between the cells to reduce interference

{{ cite news }}: Википедия:Обслуживание CS1 (множественные имена: authors list) ( ссылка ) - Peter Clarke (2014-08-25). (англ.) . EETimes. из оригинала 12 января 2015 . Дата обращения: 11 января 2015 .

- Dick James (2014-08-05). (англ.) . ChipWorks. из оригинала 1 января 2015 . Дата обращения: 11 января 2015 .

- Rick Merritt (2014-08-05). (англ.) . EETimes. из оригинала 13 января 2015 . Дата обращения: 11 января 2015 .

- Lal Shimpi, Anand (2010-12-02). . Anandtech. из оригинала 3 декабря 2010 . Дата обращения: 2 декабря 2010 .

- Ed Oswald (2012-02-20). (англ.) . ExtremeTech. из оригинала 9 января 2015 . Дата обращения: 9 января 2015 .

- Grupp, Laura M., John D. Davis,Steven Swanson. // Proceedings of the 10th USENIX conference on File and Storage Technologies. — USENIX Association, 2012. 6 сентября 2015 года.

- Kim, Kinam; Koh, Gwan-Hyeob. (англ.) . — Serbia and Montenegro: Proceedings of the 24th International Conference on Microelectronics, 2004. — P. 377—384.

- Tom Coughlin; Ed Grochowski.: (англ.) . Coughlin Associates; SNIA 2014 Storage Developer Conference (15 сентября 2014). Дата обращения: 9 января 2015. 13 января 2015 года.

- от 16 мая 2022 на Wayback Machine // Nanoscale Res Lett. 2014; 9(1): 526. Sep 25, 2014.

- . Дата обращения: 22 марта 2013. 24 июня 2016 года.

- . Дата обращения: 12 декабря 2007. Архивировано из 5 декабря 2012 года.

- . Дата обращения: 12 декабря 2007. Архивировано из 12 сентября 2012 года.

- [ . Дата обращения: 12 июня 2012. Архивировано из 27 апреля 2012 года. «Из восьми /кристаллов/ можно сформировать чип флеш-памяти на 128 Гб (Eight can be combined to produce … 128GB flash memory chip)» (англ.) ]

- . Дата обращения: 12 декабря 2007. 23 мая 2006 года.

- от 16 февраля 2009 на Wayback Machine // BBC NEWS, UK, 1 april 2003

- . Дата обращения: 12 декабря 2007. Архивировано из 28 ноября 2007 года.

- ↑ (англ.) . 2012 NAND Flash market annual report. Industry analysis report . ChinaFlashMarket.com (13 января 2013). Дата обращения: 9 января 2015. 1 августа 2014 года.

- . Дата обращения: 12 декабря 2007. Архивировано из 16 октября 2007 года.

- (англ.) . 2012 NAND Flash market annual report. Industry analysis report . ChinaFlashMarket.com (13 января 2013). Дата обращения: 9 января 2015. 1 августа 2014 года.

Ссылки

- // iXBT , 2004

- 2021-09-22

- 1