Защищённый телекоммуникационный шкаф

- 1 year ago

- 0

- 0

Защищённый режим (режим защищённой виртуальной адресации) — режим работы x86-совместимых процессоров . Частично был реализован уже в процессоре 80286 , но там существенно отличался способ работы с памятью, так как процессоры ещё были 16-битными и не была реализована страничная организация памяти . Первая 32-битная реализация защищённого режима — процессор Intel 80386 . Применяется в совместимых процессорах других производителей. Данный режим используется в современных многозадачных операционных системах, Windows , Linux , macOS .

Похожий режим применялся фирмой Digital Equipment (DEC) для 32-разрядных компьютеров: VAX-11 .

В процессоре 80286 , помимо реального режима , был реализован также защищённый режим. В защищённом режиме процессор может адресовать до 16 Мбайт физической памяти и 1 Гбайт виртуальной (16384 сегмента по 64 кбайт) за счёт изменения механизма адресации. Переключение из реального режима в защищённый происходит программно и относительно просто, однако для обратного перехода необходим аппаратный сброс процессора. Для отслеживания текущего режима работы процессора используется регистр слова состояния машины (MSW). Программы реального режима без модификаций в защищённом режиме исполняться не могут, так же как и программы BIOS машины.

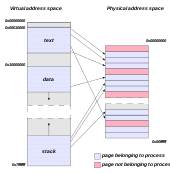

Суть защищённого режима в следующем: программист и разрабатываемые им программы используют логическое адресное пространство, размер которого может составлять 1 гигабайт. Логический адрес преобразуется в физический адрес автоматически с помощью схемы управления памятью (MMU). При этом содержимое сегментного регистра не связано напрямую с физическим адресом, а является номером сегмента в соответствующей таблице. Благодаря защищённому режиму, в памяти может храниться только та часть программы, которая необходима в данный момент, а остальная часть может храниться во внешней памяти (например, на жёстком диске). В случае обращения к той части программы, которой нет в памяти в данный момент, операционная система может приостановить программу, загрузить требуемую секцию кода из внешней памяти и возобновить выполнение программы. Следовательно, становятся допустимыми программы, размер которых больше объёма имеющейся памяти, и пользователю кажется, что он работает с большей памятью, чем на самом деле.

Физический адрес формируется следующим образом. В сегментных регистрах хранится , содержащий индекс дескриптора в таблице дескрипторов (13 бит), 1 бит, определяющий к какой таблице дескрипторов будет производиться обращение (к локальной или к глобальной) и 2 бита запрашиваемого уровня привилегий. Далее происходит обращение к соответствующей таблице дескрипторов и соответствующему дескриптору, который содержит начальный 24-битный адрес сегмента , размер сегмента и права доступа, после чего вычисляется необходимый физический адрес путём сложения адреса сегмента со смещением из 16-разрядного регистра.

С появлением 32-разрядных процессоров 80386 фирмы Intel процессоры могут работать в трёх режимах: реальном , защищённом и виртуального процессора 8086.

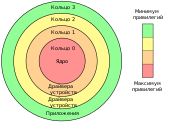

В защищённом режиме используются полные возможности 32-разрядного процессора — обеспечивается непосредственный доступ к 4 Гбайт физического адресного пространства и многозадачный режим с параллельным выполнением нескольких программ ( процессов ). Собственно говоря, многозадачный режим организует многозадачная операционная система, однако микропроцессор предоставляет необходимый для этого режима надежный механизм защиты задач друг от друга с помощью четырёхуровневой системы привилегий . Также в этом режиме доступна страничная организация памяти, повышающая уровень защиты задач друг от друга и эффективность их выполнения.

В процессоре i386 компания Intel учла необходимость лучшей поддержки реального режима, потому что программное обеспечение к времени его появления не было готово полностью работать в защищённом режиме. Поэтому, например, в i386, возможно переключение из защищённого режима обратно в реальный (при разработке 80286 считалось, что это не потребуется, поэтому на компьютерах с процессором 80286 возврат в реальный режим осуществляется схемно — через сброс процессора).

При включении микропроцессора в нём автоматически устанавливается режим реального адреса. Переход в защищённый режим осуществляется программно путём выполнения соответствующей последовательности команд. Программы, предназначенные для защищённого режима, должны быть написаны особым образом. Это означает, что реальный и защищённый режим несовместимы.

Вся физическая память делится на страницы фиксированного размера (4 К Байт , 2 МБ или 4 МБ, в x86_64 также 1 ГБ). Каждая страница, независимо от размера, выравнена по границе 4 К Байт .

Основная мысль сводится к формированию таблиц описания памяти, которые определяют состояние её отдельных сегментов/страниц и т. п. При нехватке памяти операционная система может выгрузить часть данных из оперативной памяти на диск, а в таблицу описаний внести указание на отсутствие этих данных в памяти. При попытке обращения к отсутствующим данным процессор сформирует исключение #PF (разновидность прерывания) и отдаст управление операционной системе, которая вернёт данные в память, а затем вернёт управление программе. Таким образом для программ процесс подкачки данных с дисков происходит незаметно.

Линейная адресация памяти — схема адресации памяти компьютера в защищённом режиме (начиная с Intel 80386 и других совместимых x86-процессорах). Используется большинством современных многозадачных ОС.

Благодаря механизму линейной адресации можно создавать любое (ограниченное только размерами оперативной памяти ) количество независимых виртуальных адресных пространств . Причём каждая страница линейного адресного пространства может находиться по любому физическому адресу или даже быть выгруженной на диск.

При использовании линейной адресации 32- битный логический адрес делится на три части:

При использовании страниц по 4 М Байт вторая часть отсутствует. Смещение же в странице будут определять биты 21-0 (22 бита).

Для включения линейной адресации необходимо, находясь в защищённом режиме, установить бит PG в регистре . Предварительно необходимо создать в памяти ( англ. Page Directory , PD) и таблицы страниц ( англ. Page Table , PT), после чего в регистр загрузить физический адрес каталога страниц .

Обе эти структуры представляют собой таблицы элементов каталога и таблицы страниц ( англ. Page Directory Entry , PDE и англ. Page Table Entry , PTE) страницы памяти по 4 К Байт .

Оба элемента занимают по 4 байта (32 бита ) и имеют похожую структуру:

В жёлтых полях (Page table address, Page address) записаны старшие 20 бит адреса таблицы страниц и страницы соответственно (младшие 12 бит физического адреса всегда равны нулю — не забывайте о выравнивании).

Три бита Avl — это биты , отданные системе. В них можно записать всё что угодно.

Описание флагов: