Блок управления памятью

- 1 year ago

- 0

- 0

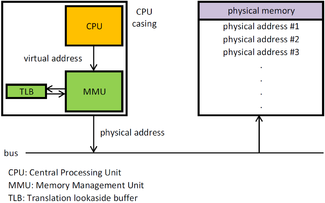

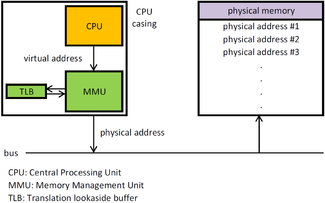

Блок управления памятью или устройство управления памятью ( англ. memory management unit , MMU) — компонент аппаратного обеспечения компьютера , отвечающий за управление доступом к памяти , запрашиваемым центральным процессором .

Его функции заключаются в трансляции адресов виртуальной памяти в адреса физической памяти (то есть управление виртуальной памятью ), защите памяти , управлении кэш -памятью, арбитражем шины и, в более простых компьютерных архитектурах (особенно с небольшой разрядностью шины адреса), переключением блоков памяти. Иногда также упоминается как блок управления страничной памятью ( англ. Paged memory management unit , PMMU).

В настоящее время чаще всего упоминается в связи с организацией виртуальной памяти и, следовательно, критически важен для многих современных многозадачных операционных систем , включая все современные Windows NT и многие из UNIX ‐подобных. Специальная редакция ядра Linux , μClinux , может работать без MMU.

Блок управления памятью в настоящее время очень часто включается в состав центрального процессора или чипсета компьютера.

Принцип работы современных MMU основан на разделении виртуального адресного пространства (одномерного массива адресов, используемых центральным процессором) на участки одинакового, как правило, несколько килобайт , хотя, возможно, и существенно большего, размера, равного степени 2, называемые страницами . Младшие n бит адреса (смещение внутри страницы) остаются неизменными. Старшие биты адреса представляют собой номер (виртуальной) страницы. MMU обычно преобразует номера виртуальных страниц в номера физических страниц, используя буфер ассоциативной трансляции ( англ. Translation Lookaside Buffer, TLB ).

Если преобразование при помощи TLB невозможно, включается более медленный механизм преобразования, основанный на специфическом аппаратном обеспечении или на программных системных структурах. Данные в этих структурах, как правило, называются элементами таблицы страниц ( англ. page table entries (PTE) ), а сами структуры — таблицами страниц ( англ. page table (PT) ). Конкатенация номера физической страницы со смещением внутри страницы даёт физический адрес.

Элементы PTE или TLB могут также содержать дополнительную информацию: бит признака записи в страницу ( англ. dirty bit ), время последнего доступа к странице ( англ. accessed bit , для реализации алгоритма замещения страниц наиболее давно использованный ( англ. least recently used, LRU ), какие процессы ( пользовательские ( англ. user mode ) или системные ( англ. supervisor mode )) могут читать или записывать данные в страницу, необходимо ли кэшировать страницу.

|

|

В статье

не хватает

ссылок на источники

(см.

рекомендации по поиску

).

|