Технологический процесс в электронной промышленности

- 1 year ago

- 0

- 0

Технологический процесс полупроводникового производства — технологический процесс по изготовлению полупроводниковых (п/п) изделий и материалов; часть производственного процесса по изготовлению п/п изделий ( транзисторов , диодов и т. п.); состоит из: последовательности технологических (обработка, сборка) и контрольных операций.

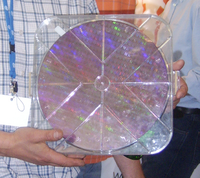

При производстве п/п изделий применяется фотолитография и литографическое оборудование . Разрешающая способность (в мкм и нм ) этого оборудования (т. н. проектные нормы ) и определяет название применяемого конкретного технологического процесса.

Совершенствование технологии и пропорциональное уменьшение размеров п/п структур способствуют улучшению характеристик (размеры, энергопотребление, рабочие частоты, стоимость) полупроводниковых приборов ( микросхем , процессоров , микроконтроллеров и т. д.). Особую значимость это имеет для процессорных ядер , в аспектах потребления электроэнергии и повышения производительности, поэтому ниже указаны процессоры (ядра) массового производства на данном техпроцессе.

Технологический процесс производства полупроводниковых приборов и интегральных микросхем ( микропроцессоров , модулей памяти и др.) включает нижеследующие операции.

Технологии производства полупроводниковой продукции с субмикронными размерами элементов основаны на чрезвычайно широком круге сложных физико-химических процессов: получение тонких плёнок термическим и ионно-плазменным распылением в вакууме, механическая обработка пластин производится по 14-му классу чистоты с отклонением от плоскостности не более 1 мкм, широко применяется ультразвук и лазерное излучение , используются отжиг в кислороде и водороде, рабочие температуры при плавлении металлов достигают более 1500 °C, при этом диффузионные печи поддерживают температуру с точностью 0,5 °C, широко применяются опасные химические элементы и соединения (например, белый фосфор ).

Всё это обусловливает особые требования к производственной гигиене, так называемую «электронную гигиену», ведь в рабочей зоне обработки полупроводниковых пластин или на операциях сборки кристалла не должно быть более пяти пылинок размером 0,5 мкм в 1 л воздуха. Поэтому в чистых комнатах на фабриках по производству подобных изделий все работники обязаны носить специальные комбинезоны . В рекламных материалах Intel спецодежда работников получила название bunny suit («костюм кролика») .

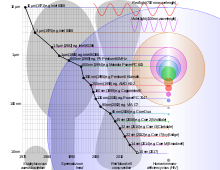

Ранние техпроцессы, до стандартизации NTRS (National Technology Roadmap for Semiconductors) и ITRS , обозначались «xx мкм» (xx микрон), где xx сперва обозначало техническое разрешение литографического оборудования, затем стало обозначать длину затвора транзистора, полушаг линий металла (half pitch) и ширину линий металла. В 1970-х существовало несколько техпроцессов, в частности 20, 10, 8, 6, 4, 3, 2 мкм; в среднем, каждые три года происходило уменьшение шага с коэффициентом 0,7

3 мкм — техпроцесс, соответствующий уровню технологии, достигнутому в 1975 году Zilog ( Z80 ) и в 1979 году Intel ( Intel 8086 ). Соответствует линейному разрешению литографического оборудования, примерно равному 3 мкм.

1,5 мкм — техпроцесс, соответствующий уровню технологии, достигнутому Intel в 1982 году. Соответствует линейному разрешению литографического оборудования, примерно равному 1,5 мкм.

0,8 мкм — техпроцесс, соответствующий уровню технологии, достигнутому в конце 1980-х — начале 1990-х годов компаниями Intel и IBM .

Техпроцесс, достигнутый производственными мощностями компаниями Intel и IBM в 1994—1995 годах.

Обозначения для техпроцессов, внедренных начиная с середины 1990-х годов, были стандартизованы NTRS и ITRS и стали называться «Technology Node» или «Cycle». Реальные размеры затворов транзисторов логических схем стали несколько меньше, чем обозначено в названии техпроцессов 350 нм — 45 нм благодаря внедрению технологий resist-pattern-thinning и resist ashing . С этих пор коммерческие названия техпроцессов перестали соответствовать длине затвора .

С переходом на следующий техпроцесс ITRS площадь, занимаемая стандартной ячейкой 1 бита памяти SRAM, в среднем уменьшалась вдвое. В период с 1995 по 2008 года такое удвоение плотности транзисторов происходило в среднем каждые 2 года .

350 нм — техпроцесс, соответствующий уровню технологии, достигнутому в 1995—1997 годах ведущими компаниями — производителями микросхем, такими как Intel, IBM, и TSMC . Соответствует линейному разрешению литографического оборудования, примерно равному 0,35 мкм.

250 нм — техпроцесс, соответствующий уровню технологии, достигнутому в 1998 году ведущими компаниями — производителями микросхем. Соответствует линейному разрешению литографического оборудования, примерно равному 0,25 мкм.

Используется до 6 слоёв металла, минимальное количество литографических масок — 22 [ источник не указан 3214 дней ] .

180 нм — техпроцесс, соответствующий уровню технологии, достигнутому в 1999 году ведущими компаниями — производителями микросхем. Соответствует удвоению плотности размещения по отношению к предыдущему техпроцессу 0,25 мкм. Также впервые используются внутренние соединения на основе медных соединений ( ) с меньшим сопротивлением, чем у ранее применявшегося алюминия.

Содержит до 6-7 слоёв металла. Минимальное количество литографических масок — около 22 [ источник не указан 3214 дней ] .

130 нм — техпроцесс, соответствующий уровню технологии, достигнутому в 2001 году ведущими компаниями — производителями микросхем. В соответствии с моделями ITRS , соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 0,18 мкм.

Для обозначения более тонких техпроцессов разные технологические альянсы могут следовать различным рекомендациям (Foundry/IDM). В частности, TSMC использует обозначения 40 нм, 28 нм и 20 нм для техпроцессов, сходных по плотности с процессами Intel 45 нм, 32 нм и 22 нм соответственно .

90 нм — техпроцесс, соответствующий уровню полупроводниковой технологии, которая была достигнута к 2002 — 2003 годам . В соответствии с моделями ITRS , соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 0,13 мкм.

Технологический процесс с проектной нормой 90 нм часто используется с технологиями напряженного кремния, а также c новыми диэлектрическими материалами с низкой диэлектрической проницаемостью ( ).

65 нм — техпроцесс, соответствующий уровню технологии, достигнутому к 2004 году ведущими компаниями — производителями микросхем. В соответствии с моделями ITRS , соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 90 нм.

45 нм и 40 нм — техпроцесс, соответствующий уровню технологии, достигнутому к 2006 — 2007 годам ведущими компаниями — производителями микросхем. В соответствии с моделями ITRS , соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 65 нм.

Для микроэлектронной промышленности стал революционным, так как это был первый техпроцесс, использующий технологию high-k/metal gate (HfSiON/TaN в технологии компании Intel), для замены физически себя исчерпавших SiO 2 /poly-Si

32 нм — техпроцесс, соответствующий уровню технологии, достигнутому к 2009 — 2010 годам ведущими компаниями — производителями микросхем. В соответствии с моделями ITRS , соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 45 нм.

Осенью 2009 компания Intel находилась на этапе перехода к этому новому техпроцессу . С начала 2011 начали производиться процессоры по данному техпроцессу.

В третьем квартале 2010 года на новых мощностях расположенной на Тайване фабрики Fab 12 компании TSMC начался серийный выпуск продукции по технологии, получившей маркетинговое обозначение «28-нанометров» (не является обозначением, рекомендуемым ITRS).

В мае 2011 по технологии 28 нм фирмой Altera была выпущена самая большая в мире микросхема, состоящая из 3,9 млрд транзисторов .

22 нм — техпроцесс, соответствующий уровню технологии, достигнутому к 2009 — 2012 годам ведущими производителями микросхем. Соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 32 нм.

22-нм элементы формируются путём фотолитографии, в которой маска экспонируется светом с длиной волны 193 нм .

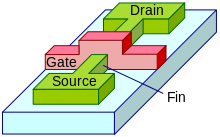

В 2008 году на ежегодной выставке высоких технологий International Electron Devices Meeting в Сан-Франциско технологический альянс компаний IBM, AMD и Toshiba продемонстрировал ячейку памяти SRAM , выполненную по 22-нм техпроцессу из транзисторов типа FinFET , которые, в свою очередь, выполняются по прогрессивной технологии high-k /metal gate (затворы транзистора изготавливаются не из кремния, а из гафния ), площадью всего 0,128 мкм² (0,58×0,22 мкм) .

Также о разработке ячейки памяти типа SRAM площадью 0,1 мкм², созданной по техпроцессу 22 нм, объявили IBM и AMD

.

Первые работоспособные тестовые образцы регулярных структур (SRAM) представлены публике компанией Intel в 2009 году

. 22-нм тестовые микросхемы представляют собой память SRAM и логические модули. SRAM-ячейки размером 0,108 и 0,092 мкм² функционируют в составе массивов по 364 млн бит. Ячейка площадью 0,108 мкм² оптимизирована для работы в низковольтной среде, а ячейка площадью 0,092 мкм² является самой миниатюрной из известных сегодня ячеек SRAM.

По такой технологии производятся (с начала 2012 года):

По состоянию на май 2014, компания Samsung продолжала разработки техпроцессов 14 нм LPE/LPP ; а выпускать процессоры для Apple планирует в 2015 году .

По состоянию на сентябрь 2014, TSMC продолжала разработку 16-нм техпроцесса на транзисторах с вертикально расположенным затвором ( Fin Field Effect Transistor , FinFET ) и планировала начать 16-нм производство в 1 квартале 2015 года .

Согласно экстенсивной стратегии фирмы Intel , уменьшение техпроцесса до 14 нм изначально ожидалось через год после представления чипа Haswell (2013); процессоры на новом техпроцессе будут использовать архитектуру с названием Broadwell . Для критических слоёв техпроцесса 14 нм Intel потребовалось применение масок с технологией Inverse Lithography (ILT) и SMO (Source Mask Optimization)

Компания МЦСТ в 2021 году представила 16-нм процессор Эльбрус-16С .

В апреле 2018 года AMD представила процессоры Zen+ на улучшенном 14-нм техпроцессе, условно обозначенном как «12 нм»:

Тайваньский производитель United Microelectronics Corporation (UMC) сообщил, что присоединится к технологическому альянсу IBM для участия в разработке 10-нм CMOS-техпроцесса .

В 2011 году публиковалась информация о планах Intel по внедрению 10-нм техпроцесса к 2018 году , в октябре 2017 Intel сообщил о планах начать производство до конца 2017 года , но в итоге, после выпуска крайне ограниченной партией 10-нм мобильного процессора Intel Core i3-8121U в 2018, массовое производство процессоров Intel по 10-нм техпроцессу началось только в 2019 году для мобильных устройств и в 2020 для десктопных.

Пробный выпуск продукции по нормам 10 нм намечался компанией TSMC на 2015 год, а серийный — на 2016 .

В начале 2017 года выпуск 10 нм составлял около 1 % от продукции TSMC

Samsung запустил 10-нм производство в 2017 году

В 2018 году на фабриках TSMC началось производство мобильных процессоров Apple A12 , Kirin 980 а также Snapdragon 855 . Производство 7-нм процессоров на архитектуре x86 задерживается, первые образцы на данной архитектуре появляются не раньше 2019 года. Согласно интернет-изданию Russian Tom’s Hardware Guide , с помощью первого поколения 7-нм техпроцесса TSMC может разместить 66 миллионов транзисторов на квадратном миллиметре, в то же время с помощью 10-нм техпроцесса Intel может разместить на аналогичной площади 100 миллионов транзисторов . Переход на второе поколение [ прояснить ] 7-нм техпроцесса у TSMC состоялся в 2019 году. Первым массовым продуктом, произведённым по этому техпроцессу, стал Apple A13 .

Intel при 7-нм техпроцессе (ожидается в 2022 году) , согласно изданию Hardwareluxx, планирует разместить 242 млн транзисторов на квадратном миллиметре .

Китайская SMIC с 2021 года выпускает 7-нм чипы на своём старом оборудовании

Продукты:

16 апреля 2019 года компания TSMC анонсировала освоение технологического процесса 6 нм в рисковом производстве, что позволяет повысить плотность упаковки элементов микросхем на 18 %, данный техпроцесс является более дешёвой альтернативной техпроцессу 5 нм, он позволяет легко масштабировать топологии, разработанные для 7 нм .

В первой половине 2019 года TSMC начала рисковое производство чипов по 5-нм техпроцессу ; переход на эту технологию позволяет повысить плотность упаковки электронных компонентов на 80 % и повысить быстродействие на 15 % . Согласно China Renaissance, техпроцесс TSMC N5 включает в себя 170 миллионов транзисторов на квадратный миллиметр .

Samsung в марте 2017 года презентовал дорожную карту по выпуску процессоров по 7- и 5-нм технологиям. В ходе презентации вице-президент Samsung по технологии Хо-Кью Кан отметил, что многие производители столкнулись с проблемой при разработке технологий меньше 10 нм. Однако Samsung справилась с задачей, ключом к которой стало использование полевого транзистора с «кольцевым» затвором ( * ). Эти транзисторы позволят компании продолжить уменьшать элементы до размера 7 и 5 нм. Для изготовления пластин компания применит технологию экстремальной ультрафиолетовой литографии (EUV) . В 2020 году Samsung начал массовое производство 5-нм чипов . Плотность техпроцесса Samsung 5LPE при этом составила 125—130 миллионов транзисторов на квадратный миллиметр .

Первым массовым продуктом, произведённым по 5-нм техпроцессу, стал Apple A14 , представленный в сентябре 2020 года. В ноябре 2020 года был представлен процессор , предназначенный для компьютеров линейки Macintosh .

В сентябре 2022 года был представлен мобильный процессор Apple A16 , выпущенный по 4 нанометрам.

Исследовательский центр ИМЕК (Бельгия) и компания Cadence Design Systems создали технологию и в начале 2018 года выпустили первые пробные образцы микропроцессоров по технологии 3 нм .

По данным TSMC , у которой 3-нанометровая топология появилась в конце 2020 году, переход на неё позволит нарастить производительность процессоров на 10— 15 % в сравнении с нынешними 5-нм чипами, а их энергопотребление снизится на 25—30 % . Ожидается, что пластина с 3-нм чипами будет стоить на 25 % больше, чем пластина 5-нм чипов .

Samsung была намерена к 2021 году начать производство 3-нанометровой продукции с использованием транзисторов с окружающим затвором (технология GAAFET) .

30 июня 2022 года Samsung заявила, что начала массовое производство 3-нм процессоров, став первой компанией, достигшей этого , но речь идет о технологии первого поколения , которая применяется для выпуска относительно простых решений для ускорения майнинга. Структурно более сложные компоненты Samsung рассчитывает выпускать уже с использованием 3-нм технологии второго поколения , которая будет освоена к 2024 году (при этом, Samsung рассчитывает превзойти конкурентов типа TSMC и Intel, перейдя на использование технологии GAAFET) .

Intel в сотрудничестве с TSMC планировала в начале 2023 года выпустить свой первый 3-нанометровый процессор (у Intel есть проект дизайна как минимум двух 3-нанометровых чипов, один из них ориентирован на ноутбуки, а второй предназначен для использования в серверах). Также к переходу на 3-нм готовится и Apple с выходом новой модификации планшета iPad Pro .

12 сентября 2023 года Apple выпустила iPhone 15 Pro и iPhone 15 Pro Max на базе 3-нм мобильных процессоров Apple A17 Pro , содержащих 19 миллиардов транзисторов .

В мае 2021 года IBM заявила о создании первого 2-нм чипа .

По словам генерального директора TSMC , в рамках перехода на 2-нм технологию упор сделан на энергетическую эффективность: скорость переключения транзисторов, непосредственно влияющая на производительность компонента, вырастет на 10—15 % при неизменном энергопотреблении, либо можно будет добиться снижения энергопотребления на 20—30 % при том же уровне быстродействия; плотность размещения транзисторов по сравнению с техпроцессом N3E вырастет только на 20 % (что ниже типичного прироста) .

2-нм чипы у TSMC (техпроцесс N2) появятся в 2026 году .

Intel в конце 2022 года заявила что после 3-нм и 1,4-нм техпроцессов будет разрабатывать 1 нм. Атом кремния имеет диаметр 0,24 нанометра, таким образом 1 нанометр соответствует 4 атомам кремния в поперечнике. Однако названия последних поколений техпроцессов являются маркетинговыми и не отражают геометрических размеров транзисторов (хотя и иллюстрируют прогресс увеличения плотности транзисторов в чипе).

В качестве средств индивидуальной защиты применяют спецодежду, изготовленную из металлизированной ткани (комбинезоны, халаты, передники, куртки с капюшонами и вмонтированными в них защитными очками)

— Городилин В. М., Городилин В. В. § 21. Излучения, их действия на окружающую среду и меры борьбы за экологию. // Регулировка радиоаппаратуры. — Издание четвёртое, исправленное и дополненное. — М. : Высшая школа, 1992. — С. 79. — ISBN 5-06-000881-9 .