Interested Article - Арифметико-логическое устройство

- 2021-03-29

- 1

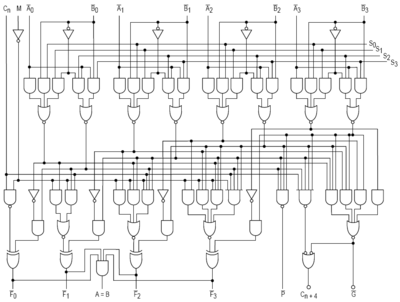

Арифме́тико-логи́ческое устро́йство ( АЛУ ; англ. arithmetic logic unit, ALU ) — блок процессора , который под управлением устройства управления служит для выполнения арифметических и логических преобразований (начиная от элементарных ) над данными, называемыми в этом случае операндами . Разрядность операндов обычно называют размером или длиной машинного слова .

Концепция арифметико-логического устройства предложена в 1945 году Джоном фон Нейманом в публикации по EDVAC ; она стала одной из составляющих ставшей классической фон-неймановской компьютерной архитектуры .

Организация и принципы действия

Арифметико-логическое устройство в зависимости от выполнения функций можно разделить на две части:

- микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

- операционное устройство, в котором реализуется заданная последовательность микрокоманд (команд).

В состав арифметико-логического устройства условно включаются регистры Рг1 — Рг7, которые служат для обработки информации, поступающей из оперативной или пассивной памяти N1, N2, … NS и логические схемы, которые используются для обработки слов по микрокомандам, поступающим из устройства управления.

Различают два вида микрокоманд: внешние — такие микрокоманды, которые поступают в АЛУ от внешних источников и вызывают в нём преобразование информации и внутренние — те, которые генерируются в АЛУ и оказывают влияние на микропрограммное устройство, изменяя таким образом нормальный порядок следования команд.

Типовые функции регистров, входящих в арифметико-логическое устройство:

- Рг1 — аккумулятор (или аккумуляторы) — главный регистр АЛУ, в котором образуется результат вычислений;

- Рг2, Рг3 — регистры операндов (слагаемого, сомножителя, делителя, делимого и других) в зависимости от выполняемой операции;

- Рг4 — регистр адреса (или адресные регистры), предназначенные для запоминания (бывает, что формирования) адреса операндов результата;

- Рг6 — k индексных регистров, содержимое которых используется для формирования адресов;

- Рг7 — l вспомогательных регистров, которые по желанию программиста могут быть аккумуляторами, индексными регистрами или использоваться для запоминания промежуточных результатов.

Часть операционных регистров могут быть адресованы в команде для выполнения операций с их содержимым, и их называют программно-доступными. К таким регистрам относятся: сумматор, индексные регистры и некоторые вспомогательные регистры. Остальные регистры нельзя адресовать в программе, то есть они являются программно-недоступными.

Операционные устройства можно классифицировать по виду обрабатываемой информации, по способу её обработки и по логической структуре.

Такая сложная логическая структура АЛУ может характеризоваться количеством отличающихся друг от друга микроопераций, которые необходимы для выполнения всего комплекса задач, поставленных перед арифметико-логическим устройством. На входе каждого регистра собраны соответствующие логические схемы, обеспечивающие такие связи между регистрами, что позволяет реализовать заданные микрооперации. Выполнение операций над словами сводится к выполнению определённых микроопераций, которые управляют передачей слов в АЛУ и действиями по преобразованию слов. Порядок выполнения микрокоманд определяется алгоритмом выполнения операций. То есть, связи между регистрами АЛУ и их функциями зависят в основном от принятой методики выполнения логических операций, в том числе арифметических или специальной арифметики.

Пример работы АЛУ на операции сложения

Функционально АЛУ состоит из двух регистров (Регистр1, Регистр 2), схемы управления и сумматора . Арифметическая операция выполняется по тактам:

- значения операнда 1, участвующего в арифметической операции по шине данных поступает в Регистр 1 или уже там находится;

- значения операнда 2, участвующего в арифметической операции по шине данных поступает в Регистр 2 или уже там находится;

- по шине инструкций поступает инструкция на выполнение операции в схему управления;

- данные из регистров поступают в сумматор, схема управления дает команду на выполнение сложения;

- результат сложения поступает в Регистр 1;

- признаки выполнения операции в АЛУ поступают в регистр флагов.

Пример работы АЛУ на операции вычитания:

- значение операнда 1, участвующего в арифметической операции по кодовой шине данных поступает в Регистр 1;

- значение операнда 2, участвующего в арифметической операции по кодовой шине данных поступает в Регистр 2;

- по кодовой шине инструкций, поступает инструкция на выполнение операции вычитания в схему управления;

- схема управления преобразовывает положительное число в отрицательное (в формате дополнительного кода до двух);

- результат преобразования операнда поступает в сумматор;

- сумматор складывает два числа;

- результат сложения поступает в Регистр 1;

- результат операции АЛУ поступает в результирующий блок.

Операции

Все выполняемые в арифметико-логическом устройстве операции являются логическими операциями (функциями), которые можно разделить на следующие группы:

- операции двоичной арифметики для чисел с фиксированной точкой;

- операции двоичной (или шестнадцатеричной) арифметики для чисел с плавающей точкой;

- операции десятичной арифметики;

- операции индексной арифметики (при модификации адресов команд);

- операции специальной арифметики;

- операции над логическими кодами (логические операции);

- операции над алфавитно-цифровыми полями.

Современные компьютеры общего назначения обычно реализуют операции всех приведённых выше групп, а малые и микроЭВМ , микропроцессоры и специализированные ЭВМ часто не имеют аппаратуры арифметики чисел с плавающей точкой, десятичной арифметики и операций над алфавитно-цифровыми полями. В этом случае эти операции выполняются специальными подпрограммами.

К арифметическим операциям относятся сложение , вычитание , вычитание модулей («короткие операции») и умножение и деление («длинные операции»). Группу логических операций составляют операции дизъюнкция (логическое ИЛИ) и конъюнкция (логическое И) над многоразрядными двоичными словами, сравнение кодов на равенство. Специальные арифметические операции включают в себя нормализацию, арифметический сдвиг (сдвигаются только цифровые разряды, знаковый разряд остаётся на месте), логический сдвиг (знаковый разряд сдвигается вместе с цифровыми разрядами). Обширна группа операций редактирования алфавитно-цифровой информации. Каждая операция в АЛУ является логической функцией или последовательностью логических функций описываемых двоичной логикой для двоичных ЭВМ, троичной логикой для троичных ЭВМ , четверичной логикой для четверичных ЭВМ, десятичной логикой для десятичных ЭВМ и так далее.

Классификация

По способу действия над операндами арифметико-логические устройства делятся на последовательные и параллельные. В последовательных устройствах операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами; в параллельных — параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов.

По способу представления чисел различают арифметико-логические устройства:

- для чисел с фиксированной точкой;

- для чисел с плавающей точкой;

- для десятичных чисел .

По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном устройстве операции над числами с фиксированной и плавающей точкой, десятичными числами и алфавитно-цифровыми полями выполняются в отдельных блоках, при этом повышается скорость работы, так как блоки могут параллельно выполнять соответствующие операции, но значительно возрастают затраты оборудования. В многофункциональных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы.

По своим функциям арифметико-логическое устройство является операционным блоком, выполняющим микрооперации, обеспечивающие приём из других устройств (например, памяти) операндов, их преобразование и выдачу результатов преобразования в другие устройства. Арифметико-логическое устройство управляется управляющим блоком, генерирующим управляющие сигналы, инициирующие выполнение в АЛУ определённых микроопераций. Генерируемая управляющим блоком последовательность сигналов определяется кодом операции команды и оповещающими сигналами.

Примечания

- Макаровой Н. В. Информатика: Учебник. — М. : Финансы и статистика, 2006. — 768 с. — ISBN 978-5-279-02202-1 .

Литература

- Каган Б. М. Электронные вычислительные машины и системы. — 3-е изд., перераб. и доп. — Энергоатомиздат, 1991. — ISBN 5-283-01531-9 .

- Угрюмов Е. П. Цифровая схемотехника. Учеб. пособие для вузов. Изд. 2. — БХВ-Петербург, 2004.

- Самофалов К. Г., Романкевич А. М., Валуйский В. Н., Каневский Ю. С., Пиневич М. М. Прикладная теория цифровых автоматов. — К. : Вища школа, 1987. — С. 375.

- Ершов А. П., Монахов В. М., Бешенков С. А. и др. 1 // Основы информатики и вычислительной техники: Проб. учеб. пособие для сред. учеб. заведений. В 2 ч. — М. : Просвещение, 1985. — С. 96.

- Ершов А. П., Монахов В. М., Кузнецов А. А. и др. 2 // Основы информатики и вычислительной техники: Проб. учеб. пособие для сред. учеб. заведений. В 2 ч. — М. : Просвещение, 1986. — С. 143.

- . Логические основы ЭВМ. Пособие к курсам «Радиоэлектроника» и «Микропроцессорные средства» . Республика Карелия, г. Петрозаводск, ПетрГУ. . Дата обращения: 18 сентября 2010. 3 июня 2004 года.

- от TestLabs.kz

|

Для улучшения этой статьи

желательно

:

|

- 2021-03-29

- 1