Interested Article - Barrel shifter

- 2020-07-17

- 1

Barrel shifter (устройство быстрого сдвига) — цифровая электронная схема , производящая сдвиг данных на указанное число позиций за один такт синхронизации . Устройство быстрого сдвига также может производить циклический сдвиг и расширение знакового бита.

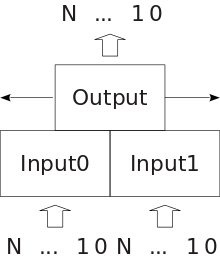

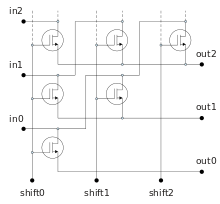

На вход устройства подаётся две группы входных данных по N бит каждая и N управляющих сигналов, на выходе получается N бит данных. Количество разрядов, на которые производится сдвиг, определяется позицией управляющего сигнала высокого уровня (все остальные управляющие сигналы должны иметь низкий уровень), выполняемая операция определяется подачей входных данных. Например:

- при подаче данных на «вход 1» и нулей на «вход 0» будет произведён правый сдвиг;

- при подаче данных на оба входа будет произведён циклический сдвиг.

Устройство быстрого сдвига применяется в целочисленных арифметических операциях (где сдвиг на один разряд эквивалентен умножению или делению на два) и в операциях над числами с плавающей запятой для выравнивания операндов при выполнении сложения и вычитания. Мантисса числа, имеющего меньший порядок, сдвигается вправо, количество позиций, на которые производится сдвиг, равно разнице порядков чисел. После сдвига порядки чисел становятся равными.

Недостатки (для barrel shift, реализующего циклический сдвиг):

- Входная ёмкость пропорциональна разрядности N.

- Количество транзисторов пропорционально квадрату разрядности N 2

- Требуется декодер для формирования управляющих сигналов.

В процессорах x86 применяются, начиная с Intel 80386.

Ресурсоёмкость

Количество мультиплексоров, необходимое для реализации n -битового устройства сдвига, по схеме barrel составляет . Для пяти часто используемых размеров количество мультиплексоров составляет:

- 128-бит —

- 64-бит —

- 32-бит —

- 16-бит —

- 8-бит —

Стоимость критического пути в единицах Fan-out-of-4 () оценивается (без учёта задержки в проводниках) как:

- 32-bit: от 18 FO4 до 14 FO4

См. также

Примечания

- : slide 6

- от 10 августа 2019 на Wayback Machine : "У 386-го процессора ... заменили последовательный регистр сдвига параллельным (barrel shifter, производит любой вид сдвига на любое число бит за фиксированное время)."

- ↑ * 2 октября 2013 года. // Proceedings of SPIT-IEEE Colloquium and International Conference, Mumbai, India Vol2, 150

- David T. Wang, от 13 марта 2012 на Wayback Machine // RealWorldTech, August 15, 2002

Литература

- Wayne Wolf. 6.2 Combinational Shifters // Modern VLSI Design: IP-Based Design. — 4th ed.. — Prentice Hall, 2009. — 627 p. — (Prentice Hall Modern Semiconductor Design Series). — ISBN 0137145004 .

Ссылки

- , Matthew R. Pillmeier

- // Proceedings of SPIT-IEEE Colloquium and International Conference, Mumbai, India Vol2, 150

- // Bill Cowan, CS251 – Spring 2008

- // Somayyeh Koohi

- 2020-07-17

- 1

. Для пяти часто используемых размеров количество мультиплексоров составляет:

. Для пяти часто используемых размеров количество мультиплексоров составляет: